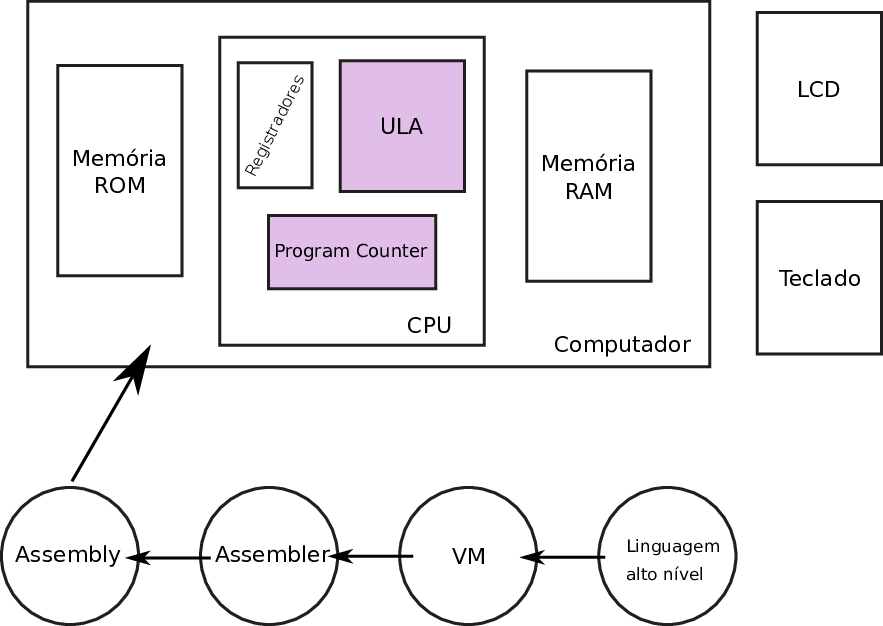

C - ULA

| Entrega |

|---|

| Sexta - 20/03 |

Neste projeto seu grupo terá que desenvolver os componentes para a implementação de uma unidade lógica e aritmética (ULA) de 16 bit (proposta pelo livro texto) que será capaz de realizar operações binárias muito simples porém que possibilitará realizarmos muitas coisas!

Warning

O grupo deve eleger um novo scrum master para essa entrega (diferente do projeto B).

Note

Nas discussões com o grupo, o scrum master deverá definir os módulos que cada integrante irá desenvolver. Crie uma rotina para commits e pull-requests.

Tip 1

Você é Scrum Master e não sabe por onde começar?

De uma olhada nessas dicas:

Vixi! Sou Scrum Master

Tip 2

Sempre teste os módulos e verifique se está funcionando como o esperado.

Instruções

A pasta do projeto C, no repositório Z01, possui a seguinte estrutura:

/c_ULA

test_ula.py

ula_cocotb.py

/Quartus

/src

*.vhd

- Quartus: Projeto Quartus que faz uso dos arquivos VHDL localizados em src/*.vhd;

- *.py: Scripts em python que automatizam a execução dos testes;

- src/*.vhd: Arquivos VHDL que serão implementados pelo grupo;

Executando o Script de Teste

Abra o terminal na pasta c_ULA/ e execute:

$ pytest -s

para testar todos os módulos ou

$ pytest -k inc16

para testar apenas um módulo (neste caso o incrementador).

O mesmo irá compilar os arquivos src/*.vhd e executar os testes unitários em cada um deles. Nesse momento do teste, como os módulos não estão implementados, o resultado deverá ser falho.

Esse comando executa um teste unitário em cada um dos módulos, verificando se sua implementação está correta. O resultado é exibido na tela como : Passed ou Failed.

O que deve ser feito:

Além de implementar os módulos, deve-se gerar uma imagem com a forma de onda de cada um desses módulos.

Note que é possível reaproveitar, via port map, os módulos do projeto anterior (C). Esses módulos anteriores já estão incluídos automaticamente (pelo script) na compilação dos módulos do projeto C.

Módulos

Note

Esses arquivos estão localizados em c_ULA/src/

Deve-se implementar os seguintes circuitos combinacionais:

-

HalfAdder

- Arquivo :

halfadder.vhd - Descrição : Adiciona dois bits que resulta em um bit de soma e outro de carry out.

- Dependência: Não tem.

- Arquivo :

-

FullAdder

- Arquivo :

fulladder.vhd - Descrição : Adiciona três bits, dois referentes às entradas e o outro referente ao carry in. O resultado é um bit com a soma e outro com o carry out.

- Dependência: Não tem.

- Arquivo :

-

Add16

- Arquivo :

add16.vhd - Descrição : Adiciona dois vetores de 16 bits resultando em um vetor de 16 bits (sem carry out do bit mais significativo - MSB).

- Dependência:

fulladder

- Arquivo :

Note

Deve utilizar o fulladder via port map.

- Inc16

- Arquivo :

inc16.vhd - Descrição : Adiciona '1' a um vetor de 16 bits resultando em um vetor de 16 bits (sem carry out).

- Dependência:

add16

- Arquivo :

Note

Deve utilizar o add16 via port map.

-

Inversor16

- Arquivo :

inversor16.vhd - Descrição : Inverte um vetor de entrada quando o bit de controle n (nx ou ny) for igual a '1', e não modifica o vetor de entrada caso contrário. O resultado é um novo vetor de 16 bits.

- Dependência: Não tem.

- Arquivo :

-

Zerador16

- Arquivo :

zerador16.vhd - Descrição : Zera um vetor de entrada quando o bit de controle z (zx ou zy) for igual a '1'. Não modifica o vetor de entrada se o bit for '0'. O resultado é um novo vetor de 16 bits.

- Dependência: Não tem.

- Arquivo :

-

Comparador16

- Arquivo :

comparador16.vhd - Descrição : Verifica se o vetor de saída (16 bits) é igual a zero (zr) e se menor que Zero (ng). Caso igual a zero, faz com que o sinal zr seja igual a '1' e caso contrário '0'. Se o sinal de entrada for negativo faz com que ng receba '1' e '0' caso contrário.

- Dependência: Não tem.

- Arquivo :

-

ALU

- Arquivo :

alu.vhd - Descrição : A entidade que faz o mapeamento de todas as demais, interligando os blocos (zerador, comparador, inversor, Add ....) em um único bloco.

- Dependência:

comparador16,zerador16,inversor16,add16,

- Arquivo :

Note

Deve utilizar os módulos via via port map.

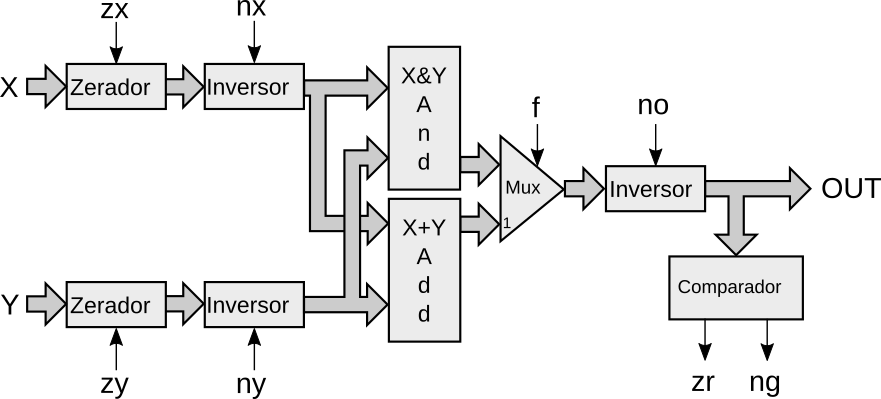

Para implementar a ALU será necessário usar os blocos desenvolvidos neste projeto e os blocos desenvolvidos no projeto anterior: and16, mux16. O script de compilação e teste já faz a inclusão deles. A arquitetura da ULA pode ser vista abaixo:

Forma de onda

Para cada teste realizado, deve-se carregar a interface gráfica e tirar um print da forma de onda do módulo com os testes aplicados a ele (Lab-6). Essa imagem deve ser salva na mesma pasta dos arquivos VHDL (src/) e com o mesmo nome dos módulos. A pasta no final do projeto deve possuir os seguintes arquivos:

/src/

add16.vhd

add16.png

alu.vhd

alu.png

comparador16.vhd

comparador16.png

fulladder.vhd

fulladder.png

halfadder.vhd

halfadder.png

inc16.vhd

inc16.png

inversor16.vhd

inversor16.png

zerador16.vhd

zerador16.png

Testando em HW

Para testar os módulos em hardware, deve-se abrir o projeto (c_ULA/Quartus). Ele já inclui todos os módulos desta entrega e também os módulos da entrega passada. O arquivo localizado em src/toplevel.vhd já faz o mapeamento dos pinos da FPGA para os pinos da ULA. Para testar no hardware basta compilar e programar a FPGA.

Rubricas para avaliação de projetos

Cada integrante do grupo irá receber duas notas: uma referente ao desenvolvimento total do projeto (Projeto) e outra referente a sua participação individual no grupo (que depende do seu papel).

Projeto

Warning

Não fazer rubrica A e B na master, criar um novo branch para isso!

| Conceito | |

|---|---|

| I | Não implementou ao menos um dos módulos Add16, ULA, Comparador, FullAdder, HalfAdder, Inc16, Inversor, Zerador. |

| D | Implementou todos os módulos menos a ULA. |

| C | Todos os modulos básicos implementados e passando nos testes |

| C+ | Todos os modulos básicos implementados e passando nos testes |

E realizar reaproveitamento dos módulos via port map sempre que possível |

|

| E obter a forma de onda de todos os módulos (.png). | |

| B+ | Todos os itens do conceito C+ implementados e funcionando |

| E modificar a ULA adicionando o sinal de estouro da soma (carry) a saída da ULA | |

| E implementar e testar a ULA com o sinal de estouro na FPGA | |

| A+ | Todos os itens do conceito C+ E B+ implementados e funcionando |

| E modificar a ULA adicionando a operação de shift left/right | |

| Para testar este último, implementar na FPGA a ULA modificada na FPGA, mostrando o resultado no 7seg |

Note

- Para os conceitos B e A, o grupo deve gravar um vídeo da FPGA demonstrando que as modificações funcionam.

-

Para os conceitos B e A, o grupo deve modificar o teste da ULA para que comprove o funcionamento dos recursos adicionados (sinais, operações), ou seja, testá-los tentando abordar todos os casos comuns de uso.

-

Os conceitos são incrementais: primeiro deve atingir o C

B

A.

Desenvolvedor e Scrum Master

As rubricas a serem seguidas serão comuns a todos os projeto e está descrito no link: